### Challenges in Testing 3D-IC Designs

Three-dimensional stacked integrated circuits (3D-ICs) are composed of multiple stacked die, and are viewed as critical in helping the semiconductor industry keep pace with Moore's Law. Current integration and interconnect methods include wirebond and flip-chip and have been in production for some time.

The next generation of 3D integration incorporates through-silicon-via (TSV) technology as the primary method of interconnect between the die. The migration to 3D-ICs connected by TSVs presents three new test challenges to the industry:

1. Managing the escape rate of defective die at wafer to meet target post-packaging yield.

2. Testing memory die stacked on logic die configurations.

3. Testing logic stacked on logic die configurations.

### Comprehensive Solutions for Known Good Die

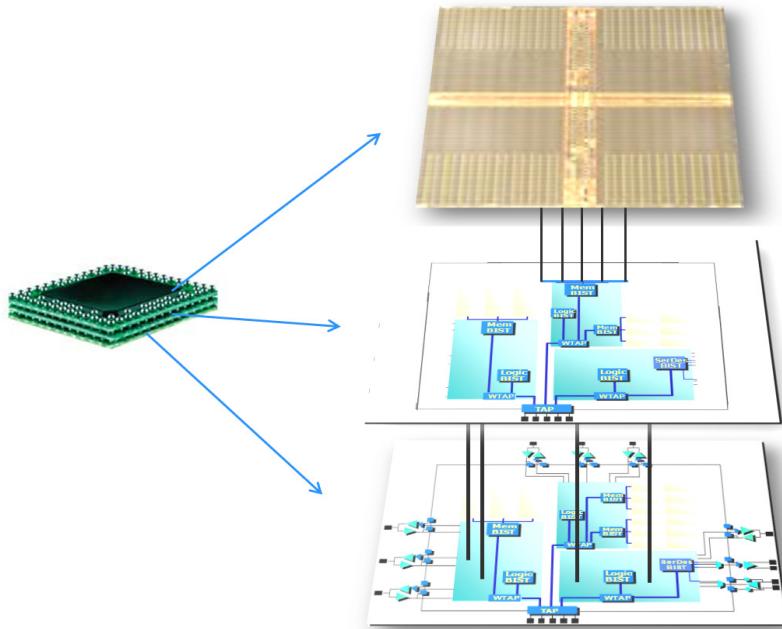

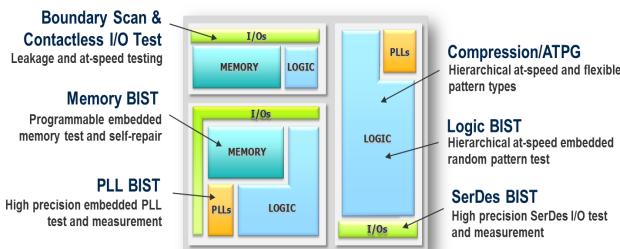

The Tessent® silicon test and yield analysis solutions provide a comprehensive set of design-for-test (DFT) capabilities that addresses the known-good-die testing challenges. These include the industry-leading solutions for ATPG, compression, logic BIST, memory BIST, boundary scan, mixed-signal BIST and silicon learning.

### Key Benefits

- Test 3D-ICs today with available Tessent® technology.

- Improve yield of stacked die with high-quality test of single die components.

- Generate test patterns for stacked die faster by retargeting existing single die patterns using the same test generation methods.

- Mentor Graphics award-winning customer support ensures success.

### Key Features

- Tessent 3D-IC support is included in the TSMC Reference Flow 12.

- Comprehensive test generation, DFT and BIST capabilities enable low-cost, high-quality test for meeting critical known-good-die (KGD) requirements.

- Programmable external memory BIST enables thorough at-speed testing of memory-to-logic TSVs.

- Hierarchical ATPG enables efficient testing of logic to logic TSVs.

The Tessent product family for silicon test and yield analysis provide solutions for 2.5D and 3D ICs

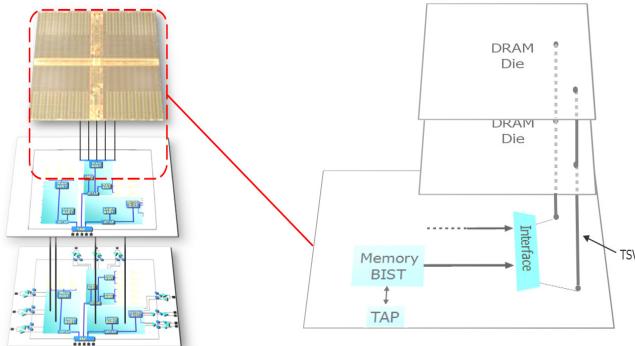

## Testing Stacked Memory-on-Logic

Using Tessent's integrated hierarchical test capabilities, high-quality tests can be implemented for stacked logic and memory die.

Tessent MemoryBIST provides at-speed testing of stacked memory die with support for all popular DRAM protocols, and allows memory parameters (address size, waveforms) and test algorithms to be programmed post-silicon. This allows memory BIST controllers in a logic die to handle a variety of memory die stacked on top for different product variations. Tessent also supports at-speed testing of memory buses, which covers both bond wires and TSV interconnects. A shared-bus capability enables test of multiple memory die on the same interconnect.

## Testing Stacked Logic-on-Logic

For logic-on-logic stacks, the Tessent hierarchical test capabilities are used to test the stacked die and the TSV interconnects.

Using Tessent solutions to test memory stacked on logic.

The ATPG and BIST tests that were generated for single die testing are reused, saving test development times. The patterns are resequenced as required to ensure correct pattern distribution and application across multiple die.

The Tessent hierarchical ATPG solution is used to test TSVs between logic die. These TSVs are assumed to exist between the boundaries of scan isolated cores on neighboring die. Test patterns are generated using the full package netlist where a graybox model is used for non-targeted die and/or cores.

By using a combination of hierarchical test architecture, high compression scan testing, and BIST technologies, the Mentor Graphics Tessent solution provides the highest quality and most economical 3D-IC testing available.

## Tessent Silicon Test and Yield Analysis Solutions

All Tessent tools are available on UNIX and Linux. For more information, visit [www.mentor.com](http://www.mentor.com).

### The Tessent Product Line

#### Logic Test

Tessent® TestKompress®

Tessent LogicBIST

Tessent SoCScan

Tessent FastScan™

Tessent BoundaryScan

#### Mixed-Signal Test

Tessent SerdesTest

Tessent PLLTest

#### Memory Test

Tessent MemoryBIST

#### Silicon Learning

Tessent SiliconInsight®

Tessent YieldInsight®

Tessent Diagnosis

For more information about 3D-IC test support, download the white paper *Testing 3D-ICs with Tessent* from [http://go.mentor.com/3D-IC\\_Test](http://go.mentor.com/3D-IC_Test)

## Visit our website at [www.mentor.com](http://www.mentor.com)

Copyright © 2011 Mentor Graphics Corporation. Mentor products and processes are registered trademarks of Mentor Graphics Corporation. All other trademarks mentioned in this document are trademarks of their respective owners.

**Corporate Headquarters**

**Mentor Graphics**

**Corporation**

8005 S.W. Boeckman Road

**Wilsonville, Oregon**

**97070-7777**

Phone: 503-685-7000

Fax: 503-685-1204

**Sales and Product**

**Information**

Phone: 800-547-3000

**Silicon Valley**

**Mentor Graphics**

**Corporation**

1001 Ridder Park Drive

San Jose, California 95131 USA

**Phone: 408-436-1500**

Fax: 408-436-1501

**North American**

**Support Center**

Phone: 800-547-4303

**Europe**

**Mentor Graphics**

**Deutschland GmbH**

Arnulfstrasse 201

80634 Munich

Germany

Phone: +49.89.57096.0

Fax: +49.89.57096.400

**Pacific Rim**

**Mentor Graphics Taiwan**

Room 1001, 10F,

International Trade Building

No. 333, Section 1, Keelung Road

Taipei, Taiwan, ROC

Phone: 886-2-87252000

Fax: 886-2-27576027

**Japan**

**Mentor Graphics Japan**

Co., Ltd.

Gotenyama Garden

7-35, Kita-Shinagawa 4-chome

Shinagawa-Ku, Tokyo 140-0001

Japan

Phone: 81-3-5488-3033

Fax: 81-3-5488-3004

**Mentor**

**Graphics**